Intel Architektura Many Integrated Core

Podczas międzynarodowej konferencji International Supercomputing Conference (ISC), Kirk Skaugen, wiceprezes firmy Intel Corporation i dyrektor generalny grupy ośrodków przetwarzania danych, przedstawił plany osiągnięcia wydajności rzędu eksaFLOP/s pod koniec tej dekady. EksaFLOP/s to trylion operacji na sekundę, setki razy więcej niż osiągają najszybsze komputery dzisiaj. Zdaniem Skaugena osiągnięcie wydajności na poziomie exascale będzie wymagać nie tylko połączenia wysiłków przemysłu i rządów, ale także podejścia zapoczątkowanego przez architekturę Intel Many Integrated Core (Intel MIC). Problemy związane z dynamicznym wzrostem ilości danych udostępnianych w Internecie, poszukiwania sposobów rozwiązań problemu zmian klimatycznych, opanowanie rosnących kosztów dostępu do surowców takich jak gaz i ropa naftowa oraz mnóstwo innych wyzwań wymaga zwiększonych zasobów obliczeniowych, co jest możliwe tylko przy zastosowaniu superkomputerów o coraz wyższej wydajności. (Dalej)...

— Choć procesory Intel Xeon są w tej chwili oczywistym wyborem dla superkomputerów z listy TOP500, Intel jeszcze silniej koncentruje się na komputerach wysokiej wydajności, przygotowując branżę do przekroczenia kolejnych barier przy wykorzystaniu architektury Many Integrated Core do obsługi obciążeń roboczych klasy petascale, a w przyszłości exascale — powiedział Skaugen. — Intel , mając dostęp do niezrównanych technologii produkcyjnych, innowacyjną architekturę i dobrze znane środowisko programistyczne przybliża nas do ekscytującego celu, jakim jest osiągnięcie wydajności klasy exascale.

Torując drogę do wydajności rzędu eksaFLOP/s

Nieustające podążanie firmy Intel za prawem Moore’a — podwajanie gęstości upakowania tranzystorów na mikroprocesorach mniej więcej co dwa lata, aby zwiększyć ich możliwości i wydajność przy równoczesnym obniżeniu kosztów — w połączeniu z innowacyjnym, wysoce wydajnym modelem tworzenia oprogramowania oraz ekstremalną skalowalnością systemu zostały wskazane przez Skaugena jako kluczowe elementy potrzebne do pokonania progu klasy petascale i wkroczenia w erę komputerów klasy exascale. Z takim wzrostem wydajności wiąże się jednak znaczący wzrost zużycia energii.

Dla przykładu najszybszy obecnie superkomputer w Chinach, Tianhe-1A, do osiągnięcia wydajności rzędu exascale potrzebowałby ponad 1,6 GW mocy — ilości energii wystarczającej do zasilania 2 milionów domów — co stanowi poważne wyzwanie z dziedziny wydajności energetycznej.

Aby rozwiązać ten problem, Intel wspólnie z europejskimi badaczami założył trzy laboratoria, przed którymi postawiono trzy główne cele: zbudowanie trwałej obecności partnerskiej w Europie, wykorzystanie rosnącego znaczenia europejskich badań nad komputerami wysokiej wydajności (HPC) oraz wykładniczy wzrost możliwości obliczeń strategicznych, inżynieryjnych i naukowych. Jednym z celów technicznych tych laboratoriów jest przygotowanie aplikacji symulacyjnych, które pozwolą rozwiązać problemy wydajności energetycznej związane z przejściem na komputery klasy exascale.

Zdaniem Skaugena przed rynkiem HPC stoją ogromne możliwości rozwoju. Podczas gdy superkomputery lat 80 zapewniały wydajność rzędu gigaFlop/s (miliardów operacji zmiennoprzecinkowych na sekundę), najwydajniejsze komputery przekroczyły obecnie tę wartość kilka milionów razy. Zwiększyło to z kolei zapotrzebowanie na procesory wykorzystywane w superkomputerach. Intel oczekuje, że do roku 2013 100 największych superkomputerów na świecie będzie wykorzystywać milion procesorów. Do roku 2015 liczba ta ulegnie podwojeniu, a do końca dekady osiągnie wartość 8 milionów. Szacowana wydajność superkomputera z pierwszego miejsca listy TOP500 w 2015 roku to 100 petaFLOP/s, zaś bariera 1 eksaFLOP/s zostanie pokonana w 2018 roku. Do końca dekady najszybszy system na Ziemi zgodnie z prognozami będzie miał wydajność przekraczającą 4 eksaFLOP/s.

Rozmach rozwiązań programistycznych dla architektury Intel MIC

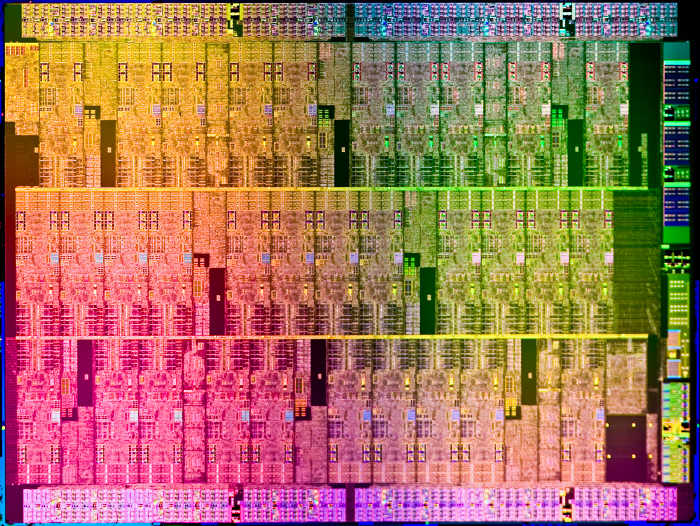

Architektura Intel MIC stanowi kluczowy dodatek do istniejących produktów firmy, w tym procesorów Intel Xeon, i oczekuje się, że pomoże wprowadzić branżę w erę wydajności klasy exascale. Pierwszy produkt Intel MIC o nazwie kodowej „Knights Corner” jest planowany do produkcji w technologii 22 nanometrów przy zastosowaniu innowacyjnych tranzystorów 3-D Tri-Gate. Intel udostępnia w tej chwili wybranym partnerom platformę do tworzenia oprogramowania dla architektury Intel MIC o nazwie kodowej „Knights Ferry”.

Podczas konferencji ISC Intel wraz z kilkoma partnerami, w tym Forschungszentrum Juelich, Leibniz Supercomputing Centre (LRZ), CERN oraz Koreańskim Instytutem Nauki i Technologii Informatycznych (KISTI) przedstawili pierwsze wyniki prac przy wykorzystaniu platformy „Knights Ferry”. Demonstracja pokazała, że architektura Intel MIC zapewnia korzyści zarówno pod względem wydajności, jak i możliwości tworzenia oprogramowania.

— Zalety modelu programistycznego architektury Intel MIC pozwoliły nam szybko przeskalować nasze aplikacje działające na procesorach Intel Xeon do platformy programistycznej Knights Ferry — powiedział prof. Arndt Bode z ośrodka obliczeniowego Leibniz Supercomputing Centre. — To obciążenie robocze zostało oryginalnie opracowane i zoptymalizowane dla procesorów Intel Xeon, ale ze względu na znajomość modelu programistycznego mogliśmy zoptymalizować kod pod kątem architektury Intel MIC w ciągu godzin i osiągnąć wydajność przekraczającą 650 GFLOPS.

Intel pokazał również platformy serwerowe i stacje robocze firmy SGI, Dell, HP, IBM, Colfax i Supermicro, które we współpracy z firmą Intel planują produkty oparte na platformie „Knights Corner”.

Superkomputery z listy TOP500

Ogłoszona podczas Konferencji ISC 37. edycja listy Top500 pokazuje, że Intel nadal pozostaje znaczącą siłą na rynku komputerów wysokiej wydajności, przy 387 systemach na liście (ponad 77 proc.) wykorzystujących procesory tej firmy. Wśród nowych systemów, które znalazły się w 2011 roku na tej liście, systemy z procesorami Intel stanowiły prawie 90 procent. Ponad połowa tych nowych komputerów wykorzystuje najnowsze procesory Intel Xeon 5600 wykonane w technologii 32 nm, na których oparte jest w tej chwili ponad 35% wszystkich systemów z listy TOP500, trzy razy więcej w porównaniu z zeszłym rokiem. W procesory firmy Intel wyposażonych jest również pięć systemów z pierwszej dziesiątki listy.

Publikowana co pół roku lista superkomputerów TOP500 stanowi dzieło Hansa Meuera z Uniwersytetu w Mannheim, Ericha Strohmaiera i Horsta Simona z krajowego ośrodka obliczeniowego badań nad energią Departamentu Energii USA oraz Jacka Dongarry z Uniwersytetu Tennessee. Pełny raport dostępny jest pod adresem www.top500.org.

Więcej informacji na temat ISC’11, w tym szczegółowy opis zaprezentowanych demonstracji architektury Intel MIC, prezentacja Skaugena oraz zdjęcia są dostępne pod adresem http://newsroom.intel.com/docs/DOC-2152.